## Introduction to ARM (Acorn/ Advanced Risc Machines)

**Gananand Kini**

June 18 2012

## Acknowledgements

- Prof. Rajeev Gandhi, Dept. ECE, Carnegie Mellon University

- Prof. Dave O'Hallaron, School of CS, Carnegie Mellon University

- Xeno Kovah

- Dana Hutchinson

- Dave Keppler

- Jim Irving

- Dave Weinstein

- Geary Sutterfield

- •

## Co-requisites

- Intro x86

- Intermediate x86 would be very helpful

## Book(s)

"ARM System Developer's Guide: Designing and Optimizing System Software" by Andrew N. Sloss, Dominic Symes, and Chris Wright

### Schedule

- Day 1 Part 1

- Intro to ARM basics

- Lab 1 (Fibonacci Lab)

- Day 1 Part 2

- More of ARMs features

- Lab 2 (BOMB Lab)

- Day 2 Part 1

- ARM hardware features

- Lab 3 (Interrupts lab)

- Day 2 Part 1.5

- GCC optimization

- Lab 4 (Control Flow Hijack Lab)

- Day 2 Part 2

- Inline and Mixed assembly

- Atomic instructions

- Lab 5 (Atomic Lab)

### **DAY 1 PART 1**

#### Introduction

- Started as a hobby in microcontrollers in high school with robotics

- Background in software development and electrical engineering

- In school, took many courses related to micro controllers and computer architecture

- Small amount of experience with assembly

## **Obligatory XKCD**

AN x64 PROCESSOR IS SCREAMING ALONG AT BILLIONS OF CYCLES PER SECOND TO RUN THE XNU KERNEL, WHICH IS FRANTICALLY WORKING THROUGH ALL THE POSIX-SPECIFIED ABSTRACTION TO CREATE THE DARWIN SYSTEM UNDERLYING OS X, WHICH IN TURN IS STRAINING ITSELF TO RUN FIREFOX AND ITS GECKO RENDERER, WHICH CREATES A PLASH OBJECT WHICH RENDERS DOZENS OF VIDEO FRAMES EVERY SECOND

BECAUSE I WANTED TO SEE A CAT JUMP INTO A BOX AND FALL OVER.

I AM A GOD.

Source: <a href="http://xkcd.com/676/">http://xkcd.com/676/</a>

#### **Short Review**

```

short ByteMyShorts[2] = \{0x3210, 0x7654\} in little endian?

Answer: 0x10325476

int NibbleMeInts = 0x4578 in binary, in octal? (no endianness involved)

Answers: 0b0100 0101 0111 1000

0b0 100 010 101 111 000

0o42570 (Take 3 bits of binary and represent in decimal)

Two's complement of 0x0113

Answer: 0xFEED

What does the following code do? (Part of output from gcc at -O3)

(%rsi), %edx

movl

movl (%rdi), %eax

xorl %edx, %eax

xorl %eax, %edx

xorl %edx, %eax

%edx, (%rsi)

movl

%eax, (%rdi)

movl

ret

```

- How can we optimize above for code size?

- Could this macro be used for atomic operations?

## We'll learn how and why

#### This turns into...

```

int main(void) {

printf("Hello world!\n");

return 0;

```

```

.syntax unified

.arch armv7-a

.eabi attribute 27, 3

.fpu vfpv3-d16

.eabi attribute 20, 1

.eabi attribute 21, 1

.eabi attribute 23, 3

.eabi attribute 24, 1

.eabi attribute 25, 1

.eabi attribute 26, 2

.eabi attribute 30, 6

.eabi attribute 18, 4

.thumb

.file "hello.c"

.section

.rodata

.align 2

.LC0:

.ascii "Hello World!\000"

.text

.align 2

.global main

.thumb

.thumb func

.type main, %function

main:

@ args = 0, pretend = 0, frame = 0

@ frame needed = 1, uses anonymous args = 0

{r7, lr}

r7, sp, #0

add

movw

r0, #:lower16:.LC0

movt

r0, #:upper16:.LC0

puts

r3, #0

mov

r0, r3

mov

{r7, pc}

pop

main, .-main

.size

.ident "GCC: (Ubuntu/Linaro 4.6.1-9ubuntu3) 4.6.1"

10

.note.GNU-stack, "", %progbits

.section

```

## And then into the following

```

Contents of section .rodata:

83ec 01000200 48656c6c 6f20576f 726c6421 ....Hello World!

00008310 <main>:

8310:

b508

push

{r3, lr}

8312:

f248 30f0

r0, #33776

movw

; 0x83f0

8316:

f2c0 0000

movt

r0, #0

831a:

f7ff efe0

blx

82dc < init+0x20>

r0. #0

831e:

2000

movs

8320:

bd08

pop

{r3, pc}

8322:

bf00

nop

00008324 < start>:

8324:

f04f 0b00

fp, #0

8328:

f04f 0e00

mov.w

lr, #0

r1, [sp], #4

832c:

f85d 1b04

ldr.w

8330:

466a

r2, sp

8332:

f84d 2d04

r2, [sp, #-4]!

str.w

r0, [sp, #-4]!

8336:

f84d 0d04

str.w

ldr.w

833a:

f8df c014

ip, [pc, #20]

; 8350 < start+0x2c>

833e:

f84d cd04

str.w

ip, [sp, #-4]!

ldr

8342:

4804

r0, [pc, #16]

; (8354 < start+0x30>)

r3, [pc, #16] ; (8358 < start+0x34>)

8344:

4b04

ldr

8346:

f7ff efd0

82e8 < init+0x2c>

834a:

f7ff efdc

blx

8304 < init+0x48>

834e:

0000

.short 0x0000

8350:

000083e1

.word

0x000083e1

8354:

00008311

.word

0x00008311

8358:

0000839d

.word

0x0000839d

```

#### Introduction to ARM

- Acorn Computers Ltd. (Cambridge, England) Nov. 1990

- First called <u>A</u>corn <u>R</u>ISC <u>M</u>achine, then <u>A</u>dvanced <u>R</u>ISC <u>M</u>achine

- Based on RISC architecture work done at UCal Berkley and Stanford

- ARM only sells licenses for its core architecture design

- Optimized for low power & performance

- VersatileExpress board with Cortex-A9 (ARMv7) core will be "emulated" using Linaro builds.

- This also means some things may not work. You've been warned.

## ARM architecture versions

| Architecture | Family                                                   |

|--------------|----------------------------------------------------------|

| ARMv1        | ARM1                                                     |

| ARMv2        | ARM2, ARM3                                               |

| ARMv3        | ARM6, ARM7                                               |

| ARMv4        | StrongARM, ARM7TDMI, ARM9TDMI                            |

| ARMv5        | ARM7EJ, ARM9E, ARM10E, Xscale                            |

| ARMv6        | ARM11, ARM Cortex-M                                      |

| ARMv7        | ARM Cortex-A, ARM Cortex-M, ARM Cortex-R                 |

| ARMv8        | Not available yet. Will support 64-bit addressing + data |

<sup>&</sup>quot;ARM Architecture." Wikipedia, The Free Encyclopedia. Wikimedia Foundation, Inc. 3 March 2012. Web. 3 March 2012.

#### **ARM Extra Features**

- Similar to RISC architecture (not purely RISC)

- Variable cycle instructions (LD/STR multiple)

- Inline barrel shifter

- 16-bit (Thumb) and 32-bit instruction sets combined called Thumb2

- Conditional execution (reduces number of branches)

- Auto-increment/decrement addressing modes

- Changed to a Modified Harvard architecture since ARM9 (ARMv5)

- Extensions (not covered in this course):

- TrustZone

- VFP, NEON & SIMD (DSP & Multimedia processing)

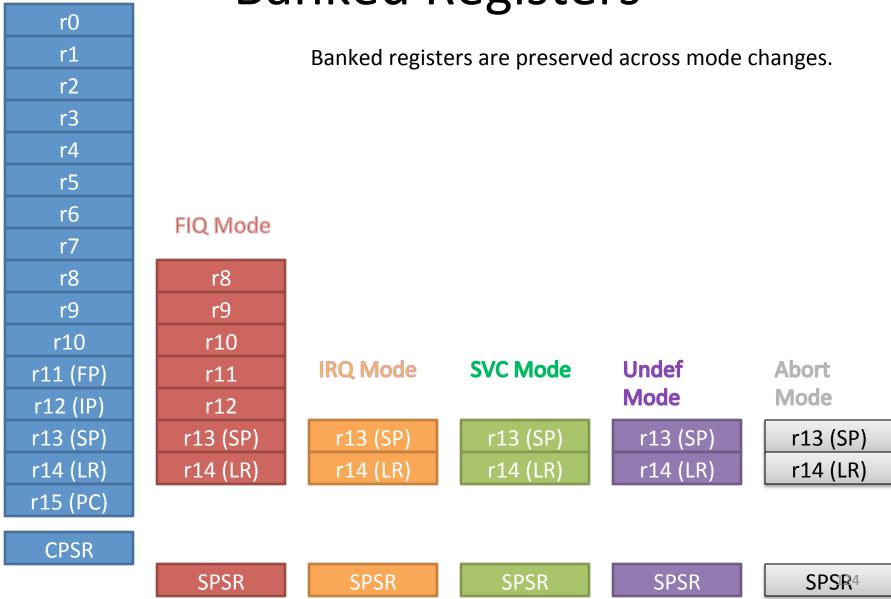

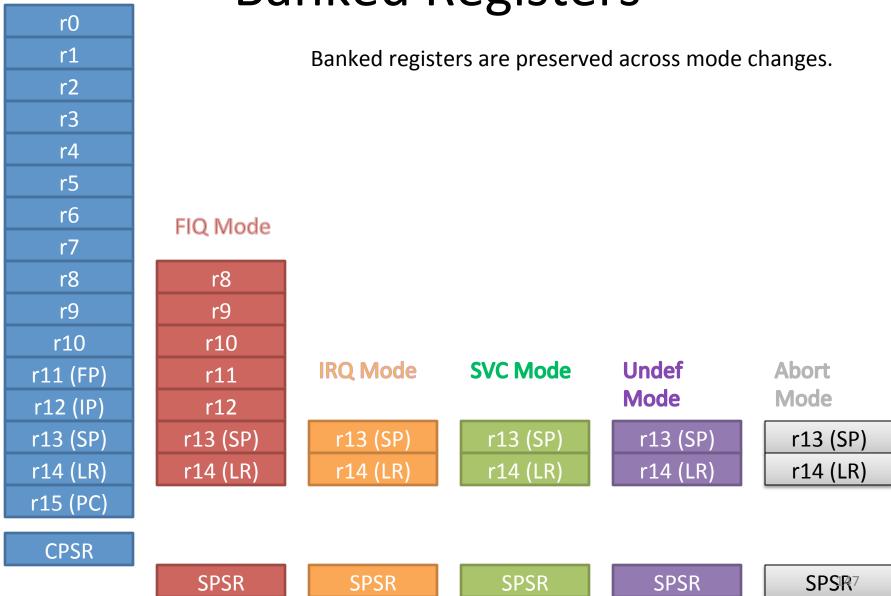

## Registers

- Total of 37 registers available (including banked registers):

- 30 general purpose registers

- 1 PC (program-counter)

- 1 CPSR (Current Program Status Register)

- 5 SPSR (Saved Program Status Register)

- The saved CPSR for each of the five exception modes

- Several exception modes

- For now we will refer to "User" mode

## Registers

r0 r1 r2 r3 r4 r5 r6 **r**7 r8 r9 R10 (SL) r11 (FP) r12 (IP) r13 (SP) r14 (LR) r15 (PC)

Stack Pointer (SP) – The address of the top element of stack.

Link Register (LR) – Register used to save the PC when entering a subroutine.

Program Counter (PC) – The address of **next** instruction. (ARM mode points to current+8 and Thumb mode points to current+4)

Current Program Status Register (CPSR) – Results of most recent operation including Flags, Interrupts (Enable/Disable) and Modes

R12 or IP is not instruction pointer, it is the intra procedural call scratch register

## Instruction cycle Start Fetch – fetch <u>next</u> instruction from memory Execute – Decode – execute fetched decode fetched instruction instruction End

#### ARM vs. x86

- Endianness (Bi-Endian)

- Instructions are little endian (except on the –R profile for ARMv7 where it is implementation defined)

- Data endianness can be mixed (depends on the E bit in CPSR)

- Fixed length instructions

- Instruction operand order is generally: OP DEST, SRC (AT&T syntax)

- Short instruction execution times

- Register differences (CPSR, SPSR...)

- Has a few extra registers

- Operations only on registers not memory (Load/Store architecture)

- Pipelining & Interrupts

- Exceptions

- Processor Modes

- Code & Compiler optimizations due to the above differences

#### ARM Data sizes and instructions

- ARMs mostly use 16-bit (Thumb) and 32-bit instruction sets

- 32-bit architecture

- Byte = 8 bits (Nibble is 4 bits) [byte or char in x86]

- Half word = 16 bits (two bytes) [word or short in MS x86]

- Word = 32 bits (four bytes) [Doubleword or int/long in MS x86]

- Double Word = 64 bits (eight bytes) [Quadword or double/long long in MS x86]

#### Source:

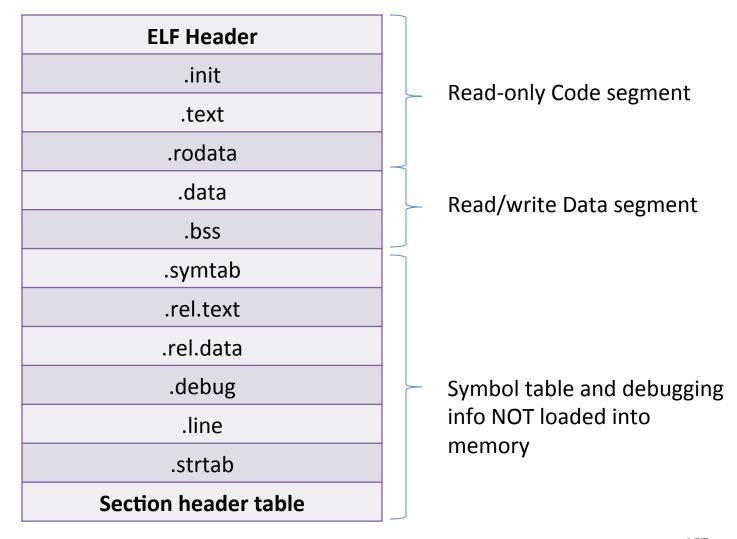

#### The Life of Binaries

- Starts with c or cpp source code written by us

- A compiler takes the source code and generates assembly instructions

- An assembler takes the assembly instructions and generates objects or .o files with machine code

- The linker takes objects and arranges them for execution and generates an executable. (A dynamic linker will insert object code during runtime in memory)

- A loader prepares the binary code and loads it into memory for OS to run

## The tools we will use

- Compiler gcc for ARM

- Assembler gcc or as (gas) for ARM

- Linker gcc for ARM or gold

- Loader gcc for ARM and Id-linux for ARM

#### At Power on...

- ROM has code that has been burned in by SoC vendor (similar to BIOS but not the same)

- Use of memory mapped IO

- different memory components (can be a mix of ROM, SRAM, SDRAM etc.)

- Contains

- Code for memory controller setup

- Hardware and peripheral init (such as clock and timer)

- A boot loader such as Fastboot, U-boot, X-Loader etc.

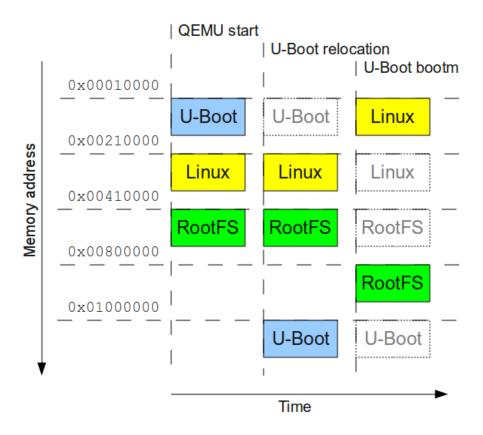

## **U-Boot process**

Source: Balducci, Francesco. <a href="http://balau82.wordpress.com/2010/04/12/booting-linux-with-u-boot-on-qemu-affn/">http://balau82.wordpress.com/2010/04/12/booting-linux-with-u-boot-on-qemu-affn/</a>

#### U-boot exercise on a Versatile PB

Run the following in ~/projects/ubootexercise:

qemu-system-arm -M versatilepb -m 128M -kernel flash.bin -serial stdio

- flash.bin contains:

- U-boot binary (at 0x10000 in image)

- a root filesystem (at 0x210000 in image)

- the linux kernel (at 0x410000 in image)

- U-boot has bootm <address> to boot code

#### **U-boot** exercise

- U-boot was patched in earlier example b/c it did not support ramdisk usage with bootm command. Good 'nough for simulation.

- U-boot uses bootm <kernel address> <rootfs image address> to boot

- U-boot relocates itself to specific address (0x1000000) before loading kernel.

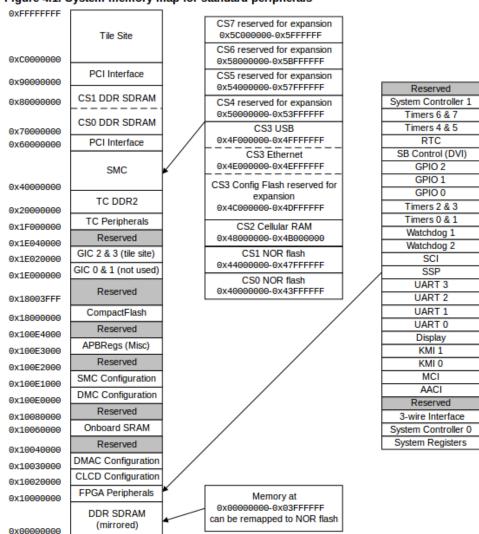

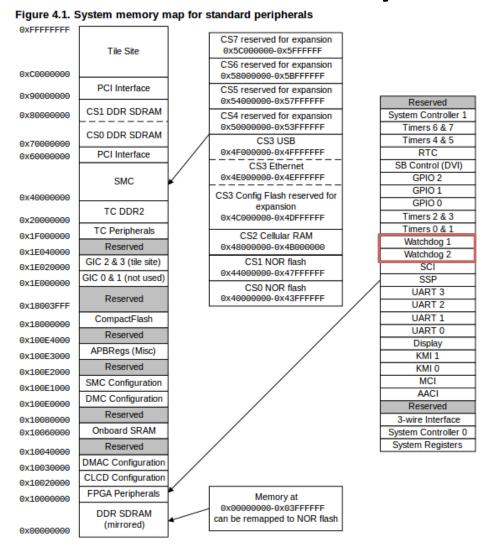

## PBX w/ Cortex-A9 Memory Map

Figure 4.1. System memory map for standard peripherals

Source:

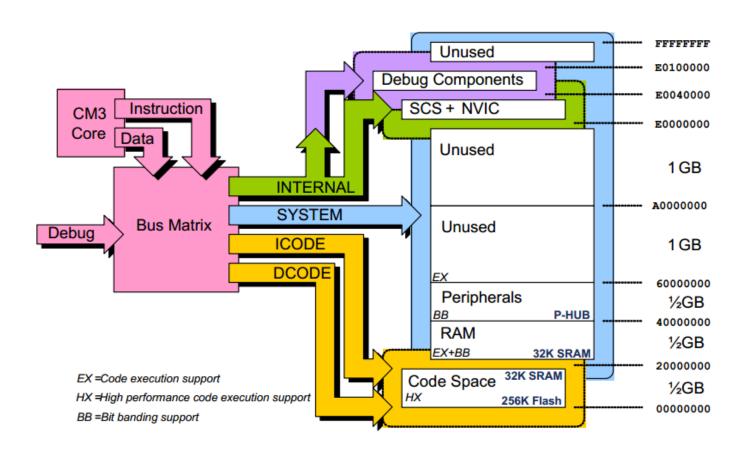

## Cortex M3 Memory Map

### **ARM Architecture**

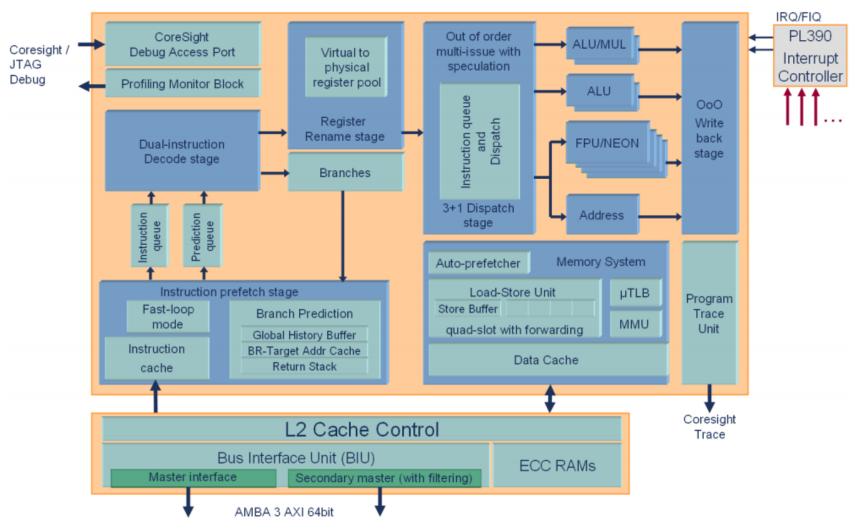

Fig. 1 Cortex-A9 microarchitecture structure and the single core interfaces.

Source: <a href="http://www.arm.com/files/pdf/armcortexa-9processors.pdf">http://www.arm.com/files/pdf/armcortexa-9processors.pdf</a>

## Instruction cycle Start Fetch – fetch <u>next</u> instruction from memory Decode – Execute – execute fetched decode fetched instruction instruction End

## Behavior of the PC/R15

- PC Program counter (like the x86 EIP) has the address of next instruction to execute

- When executing an ARM instruction, PC reads as the address of current instruction + 8

- When executing a Thumb instruction, PC reads as the address of current instruction + 4

- When PC is written to, it causes a branch to the written address

- Thumb instructions cannot access/modify PC directly

## That means...

|                       | 00008380 <add< th=""><th>d&gt;:</th><th></th><th></th></add<> | d>:       |              |              |

|-----------------------|---------------------------------------------------------------|-----------|--------------|--------------|

| When executing        | 8380:                                                         | b480      | push         | {r7}         |

| instruction @ x8382 — | >8382:                                                        | b083      | sub          | sp, #12      |

|                       | 8384:                                                         | af00      | add          | r7, sp, #0   |

| PC=0x00008386         | <del>&gt;8386</del> :                                         | 6078      | str          | r0, [r7, #4] |

|                       | 8388:                                                         | 6039      | str          | r1, [r7, #0] |

|                       | 838a:                                                         | 687a      | ldr          | r2, [r7, #4] |

|                       | 838c:683b                                                     | ldr       | r3, [r7, #0] |              |

|                       | 838e:                                                         | 18d3      | adds         | r3, r2, r3   |

|                       | 8390:                                                         | 4618      | mov          | r0, r3       |

|                       | 8392:                                                         | f107 070c | add.w        | r7, r7, #12  |

|                       | 8396:                                                         | 46bd      | mov          | sp, r7       |

|                       | 8398:                                                         | bc80      | pop          | {r7}         |

|                       | 839a:                                                         | 4770      | bx           | Ir           |

## ARM Assembly and some conventions

- Now uses Unified Assembly Language (combines ARM & Thumb instruction sets and code allowed to have intermixed instructions)

- General form (there are exceptions to this):

Instruction><Conditional>{S bit} <destination> <source> <Shift/operand/immediate value>

- Load/Store architecture means instructions only operate on registers, NOT memory

- Most of the instructions expect destination first followed by source, but not all...

# ARM Assembly and some conventions contd...

- <dst> will be destination register

- <src> will be source register

- <reg> will be any specified register

- <imm> will be immediate value

- <reg|cxfz..> whatever follows '|' means with the specified flag enabled

## **Conditional Flags**

- Indicate information about the result of an operation

- N Negative result received from ALU (Bit 31 of the result if it is two's complement signed integer)

- Z Zero flag (1 if result is zero)

- C Carry generated by ALU

- V oVerflow generated by ALU (1 means overflow)

- Q –oVerflow or saturation generated by ALU (Sticky flag; set until CPSR is overwritten manually)

- Flags are in a special register called CPSR (Current Program Status Register)

- Flags are not updated unless used with a suffix of S on instruction

# Current/Application Program Status Register (CPSR/APSR)

- N Negative flag

- Z Zero flag

- C Carry flag

- V Overflow flag

- Q Sticky overflow

- I 1: Disable IRQ mode

- F 1: Disable FIQ mode

- T 0: ARM state

- 1: Thumb state

- MODE Mode bits

## Push and Pop operations

- PUSH <reg list> decrements the SP and stores the value in <reg list> at that location

- POP <reg list> Stores the value at SP into

<reg list> and increments the SP

- Both operations only operate on SP

#### **PUSH** operation

INSTRUCTION: push {r7, lr}

0x7EFFF950

0x7EFFF954

0x7EFFF958

0x7EFFF95C

0x0a012454

0x00008350

0x0A0B0C0D

0x0a012454

0x00008350

0x00008010

0x0A0B0C0D

0x0a012454

0x00008350

SP 0x7EFFF958

**R7** 0x0A0B0C0D

LR 0x00008010 0x7EFFF954

0x0A0B0C0D

0x00008010

0x7EFFF950

0x0A0B0C0D

0x00008010

#### Arithmetic operations

- ADD: add

- <dst> = <src> + <imm> or <src> + <reg>

- ADC: add with carry

- <dst> = <src|c> + <imm> or <src|c> + <reg>

- SUB: subtract

- <dst> = <src> <imm> or <src> <reg>

- SBC: subtract with carry

- <dst> = <src | c> <imm> or <src | c> <reg>

- RSB: reverse subtract

- <dst> = <imm> <src> or <reg> <src>

- RSC: reverse subtract with carry

- <dst> = <imm|!c> <src> or <reg|!c> <src>

#### Closer look at Example 1.c

```

int main(void) {

int a, b, c;

a=10;

b=12;

c=add(a,b);

return 0;

int add(int a, int b)

return a+b;

```

The highlighted instruction is a special form of SUB. In this case means:

$$SP = SP - 16$$

Thumb instructions are intermixed with ARM instructions.

| ( | 00008354 <main>:</main>     |                     |            |                                   |  |  |  |

|---|-----------------------------|---------------------|------------|-----------------------------------|--|--|--|

|   | 8354:                       | b580                | push       | {r7, lr}                          |  |  |  |

| _ | 8356:                       | b084                | sub        | sp, #16                           |  |  |  |

|   | 8358:                       | af00                | add        | r7, sp, #0                        |  |  |  |

|   | 835a:                       | f04f 030a           | mov.w      | r3, #10                           |  |  |  |

|   | 835e:                       | 607b                | str        | r3, [r7, #4]                      |  |  |  |

|   | 8360:                       | f04f 030c           | mov.w      | r3, #12                           |  |  |  |

|   | 8364:                       | 60bb                | str        | r3, [r7, #8]                      |  |  |  |

|   | 8366:                       | 6878                | ldr        | r0, [r7, #4]                      |  |  |  |

|   | 8368:                       | 68b9                | ldr        | r1, [r7, #8]                      |  |  |  |

|   | 836a:                       | f000 f809           | bl         | 8380 <add></add>                  |  |  |  |

|   | 836e:                       | 60f8                | str        | r0, [r7, #12]                     |  |  |  |

|   | 8370:                       | f04f 0300           | mov.w      | r3, #0                            |  |  |  |

|   | 8374:                       | 4618                | mov        | r0, r3                            |  |  |  |

|   | 8376:                       | f107 0710           | add.w      | r7, r7, #16                       |  |  |  |

|   | 837a:                       | 46bd                | mov        | sp, r7                            |  |  |  |

|   | 837c:                       | bd80                | pop        | {r7, pc}                          |  |  |  |

|   | 837e:                       | bf00                | nop        |                                   |  |  |  |

| , | 20000000                    | dd>.                |            |                                   |  |  |  |

| ( | 00008380 <a<br>8380:</a<br> | uu>:<br>b480        | nuch       | (r7)                              |  |  |  |

|   |                             |                     | push       | {r7}                              |  |  |  |

|   | 8382:<br><b>8384:</b>       | b083<br><b>af00</b> | sub        | sp, #12                           |  |  |  |

|   | 8386:                       | 6078                | add        | r7, sp, #0                        |  |  |  |

|   | 8388:                       | 6039                | str<br>str | r0, [r7, #4]                      |  |  |  |

|   | 6366.<br>838a:              | 687a                |            | r1, [r7, #0]                      |  |  |  |

|   | озоа.<br>838c:              | 683b                | ldr<br>ldr | r2, [r7, #4]                      |  |  |  |

|   | 838e:                       | 18d3                | adds       | r3, [r7, #0]<br><b>r3, r2, r3</b> |  |  |  |

|   | 8390:                       | 4618                | mov        | r0, r3                            |  |  |  |

|   | 8390.<br>8392:              | f107 070c           | add.w      | r7, r7, #12                       |  |  |  |

|   | 8396:                       | 46bd                |            |                                   |  |  |  |

|   | 8398:                       | 4600<br>bc80        | mov        | sp, r7                            |  |  |  |

|   | 839a:                       | 4770                | pop<br>bx  | {r7}                              |  |  |  |

|   | ossa.                       | 4110                | UΛ         | lr                                |  |  |  |

#### SBC & RSB operations

INSTRUCTION: sbc r0, r0, r1 rsb r0, r0, r1 MEANS : r0 = r0 - r1 - NOT(C) r0 = r1 - r0 (No flags updated)

R0

0xF5F4F3FD

R1

0x0A0B0C0D

**CPSR**

0x20000010

0x0A0B0C03

0x0A0B0C0D

0x20000010

After Operation

R0

0x000000A

R1

0x0A0B0C0D

**CPSR**

0x20000010

0x000000A

0x0A0B0C0D

0x20000010

**Before Operation**

#### Arithmetic operations part 2

- MUL: <dst> = <reg1> \* <reg2>

- MLA: <dst> = (<reg1> \* <reg2>) + <reg3>

- MLA{S}{<c>} <Rd>, <Rn>, <Rm>, <Ra> where <Rd> is destination register, <Rn> & <Rm> are the first and second operands respectively and <Ra> is the addend register

- MLS: <dst> = <reg3> (<reg1> \* <reg2>)

- Multiply operations only store least significant 32 bits of result into destination

- Result is not dependent on whether the source register values are signed or unsigned values

## example2.c

```

int main(void) {

int a, b, c, d;

a=2;

b=3;

c=4;

d = multiply(a,b);

printf("a * b is %d\n", d);

d = multiplyadd(a,b,c);

printf("a * b + c is %d\n", d);

return 0;

int multiply(int a, int b)

return (a*b);

Int multiplyadd(int a, int b, int c)

return ((a*b)+c);

```

```

000083b8 <multiply>:

83b8:

fb01 f000 mul.w

r0, r1, r0

83bc:

4770

bx

lr

83be:

bf00

nop

000083c0 <multiplyadd>:

83c0:

fb01 2000 mla

r0, r1, r0, r2

83c4:

4770

bx

lr

83c6:

bf00

nop

```

#### MLA & MLS operations

INSTRUCTION: mla r0, r0, r1, r2

MEANS : r0 = r0 \* r1 + r2

mls r0, r0, r1, r2 r0 = r2 - (r0 \* r1) (No flags updated)

R0

0x0000008F

R1

0x0000000E

R2

0x00000003

CPSR

0x20000010

OxFFFFF77

Ox000000E

Ox0000003

Ox20000010

After Operation

R0

0x0000000A

R1

0x0000000E

R2

0x00000003

CPSR

0x20000010

0x000000A

0x0000000E

0x00000003

0x20000010

**Before Operation**

#### Arithmetic operations part 3

PLEASE NOTE: These instructions are only available on Cortex-R profile

- SDIV Signed divide

- UDIV Unsigned divide

- On the Cortex-A profile there is no divide operation

#### Example x.s

```

000083e4 <divide>:

r0, r0, r1

sdiv

83e4: e710f110

83e8: e12fff1e bx

lr

83ec: e1a00000

; (mov

nop

r0, r0)

000083f0 <unsigneddivide>:

83f0: e730f110

r0, r0, r1

udiv

83f4: e12fff1e bx

lr

83f8: e1a00000

; (mov

nop

r0, r0)

```

#### Using the emulator

- cd ~/projects/linaro

- ./startsim

- Password is passw0rd

- To copy <localfile> to </path/to/file> on emulator:

- scp –P 2200 <localfile> root@localhost:</path/to/file>

- To copy </path/to/file> from emulator to <localfile>:

- scp –P 2200 root@localhost:</path/to/file> <localfile>

#### objdump introduction

- dumps the objects in an ELF (Executable Linkable Format) file.

- objects that are in a form before they are linked

- -g gdb option for gcc adds debug symbols that objdump can read

- -d option for <u>objdump</u> used for dissassembling (get assembly code from the ELF format)

# objdump usage

#### helloworld.c

```

int main(void) {

printf("Hello world!\n");

return 0;

}

```

#### objdump -d helloworld | less

```

Contents of section .rodata:

83ec 01000200 48656c6c 6f20576f 726c6421 ....Hello World!

83fc 00000000

00008310 <main>:

8310:

b508

{r3, lr}

push

8312:

f248 30f0

movw

r0. #33776

: 0x83f0

8316:

f2c0 0000

r0, #0

movt

82dc < init+0x20>

831a:

f7ff efe0

831e:

2000

movs

r0, #0

8320:

bd08

{r3, pc}

pop

8322:

bf00

nop

00008324 < start>:

8324:

f04f 0b00

mov.w

fp, #0

8328:

lr, #0

f04f 0e00

mov.w

832c:

f85d 1b04

ldr.w

r1, [sp], #4

8330:

466a

r2, sp

8332:

f84d 2d04

str.w r2, [sp, #-4]!

8336:

f84d 0d04

str.w r0, [sp, #-4]!

833a:

f8df c014

ldr.w ip, [pc, #20]

; 8350 < start+0x2c>

833e:

f84d cd04

str.w ip, [sp, #-4]!

8342:

4804

ldr

r0, [pc, #16]

; (8354 < start+0x30>)

8344:

4b04

r3, [pc, #16] ; (8358 < start+0x34>)

8346:

f7ff efd0

blx

82e8 < init+0x2c>

f7ff efdc

blx

8304 < init+0x48>

834a:

834e:

0000

.short 0x0000

8350:

000083e1

.word

0x000083e1

00008311

.word

0x00008311

8354:

8358:

0000839d

.word

0x0000839d

```

#### Try dividing now on the emulator

- Goto ~/projects/examples

- Copy example1 to divexample

- Replace the add () function in example1.c with divide and return (a/b)

- Run make clobber && make

- Disassemble...

- objdump –d example1 | less

- What do you see?

#### **NOP Instruction**

- A most interesting instruction considering it does nothing

- ARM Reference Manual mentions that this instruction does not relate to code execution time (It can increase, decrease or leave the execution time unchanged).

Why?

- Primary purpose is for instruction alignment. (ARM and Thumb instructions together... What could go wrong?)

- Can also be used as part of vector tables

- In some microcontrollers, it is also used for synchronization of pipeline.

#### **Barrel Shifter**

- Hardware optimization inline with the ALU allows for a multiplier (power of 2) within same instruction cycle

- Allows for shifting a register value by either an unsigned integer (MAXVAL of 32) or a value specified in bottom byte of another register.

- ASR Arithmetic Shift Right (MSB copied at left, last bit off right is Carry)

- LSL Logical Shift Left (Os at right, last bit off left is Carry)

- MOV R7, R5, LSL #2 means (R7=R5\*4) or (R5<<2)</li>

- ADD R0, R1, R1, LSL #1 means R0=R1+(R1<<1)</p>

- LSR Logical Shift Right (0s at left, last bit off right is Carry)

- ROR Rotate Right (bits popped off the right end, is directly pushed into left, last bit off right is Carry)

- RRX Rotate Right with Extend (bits popped off the right end first go into Carry, Carry is shifted in to left, last bit off right is Carry)

#### Hints on how to RTFM

- {S} updates flags in the CPSR

- {<c>} allows mnemonic of conditional to be added

- {<q>} instruction suffix with either:

- N Narrow, assembler must use 16-bit encoding for the intruction

- .W Wide, assembler must use 32-bit encoding for the instruction

- Do <u>not</u> use the .N or .W in your assembly code.

- As per manual, it will throw errors. GNU Assembler decides on encoding depending on options selected.

#### Example 3.1.c

```

int main(void)

00008318 <main>:

8318:

b508

{r3, lr}

push

831a:

2001

r0, #1

int a, b, d;

movs

a = 6;

831c:

22c0

r2, #192

; 0xc0

movs

831e:

b = 8:

f248 4100 movw

r1, #33792; 0x8400

8322:

f2c0 0100 movt

d = multiplybytwo(a) * multiplybytwo(b);

r1, #0

8326:

printf("2a * 2b is %d\n", d);

f7ff efec

8300 < init+0x3c>

blx

832a:

2000

r0, #0

movs

return 0;

832c:

bd08

{r3, pc}

pop

832e:

bf00

nop

000083a8 <multiplybytwo>:

int multiplybytwo(int a)

83a8:

0040

Isls

r0, r0, #1

83aa:

4770

bx

lr

return a*2;

```

#### Example 3.2.c

```

int main(void)

00008318 <main>:

8318:

b508

push

{r3, lr}

831a:

2001

r0, #1

int a, b, d;

movs

a = -6;

831c:

2200

r2, #0

movs

b = 8:

831e:

f248 4104

movw

r1, #33796; 0x8404

d = dividebytwo(a) / dividebytwo(b);

8322:

f2c0 0100

r1, #0

movt

printf("a/2 / b/2 is %d\n", d);

8326:

f7ff efec

8300 < init+0x3c>

blx

832a:

2000

r0, #0

movs

return 0;

832c:

bd08

{r3, pc}

pop

832e:

bf00

nop

int dividebytwo(int a)

000083a8 < dividebytwo >:

83a8:

eb00 70d0 add.w

r0, r0, r0, Isr #31

r0, r0, #1

return a/2;

83ac:

1040

asrs

83ae:

4770

bx

```

# Example 3.2.c

| add.w r0, r0, r0, lsr #31 |            |           |            | r0, r0, #1 |

|---------------------------|------------|-----------|------------|------------|

| RO                        | 0xFFFFFF9  | RO        | 0xFFFFFFC  |            |

| R1                        | 0x0000000E | R1        | 0x000      | 0000E      |

| R2                        | 0x00000003 | R2        | 0x000      | 00003      |

| CPSR                      | 0xA0000010 | CPSR      | 0xA0000010 |            |

|                           |            |           |            |            |

| R0                        | 0xFFFFFF8  | RO        | 0x0000     | 1000       |

| R1                        | 0x000000E  | 0x000000E |            | 0000E      |

| R2                        | 0x0000003  | R2        | 0x0000     | 00003      |

| CPSR                      | 0x20000010 | CPSR      | 0x2000     | 00010      |

|                           |            |           |            |            |

#### **RRX & LSL operation**

INSTRUCTION: mvn r0, r0, RRX

MEANS :  $r0 = {^{\sim}}r0 >> 1$

add r0, r0, r1, LSL #4 r0 = r0 + (r1 \* 16) (No flags updated)

R0

OxFFFFFFA

R1

0x0000000E

R2

0x00000003

CPSR

0xA0000010

0x000000EA

0x0000000E

0x00000003

0x20000010

0x000000A

0x0000000E

0x00000003

0x20000010

# More Data operations

- MOV move value from one register to another

Combine with postfixes to modify:

- MOVT: Moves only top half word into destination without changing lower half word

- MOVS PC,<reg>: Moves value into destination register and updates CPSR flags

- MVN Bitwise NOT of value into destination register

- Cannot be used on memory locations

#### Example 4.c

```

int main(void)

00008318 <main>:

8318:

b508

push

{r3, lr}

831a:

2001

r0, #1

int a, b, d;

movs

a = 221412523;

831c:

f248 4108 movw

r1, #33800; 0x8408

b = 3:

f247 6201 movw

8320:

r2, #30209 ; 0x7601

f2c0 0100 movt

d = multiply(a,b);

8324:

r1, #0

printf("a * b is %d\n", d);

8328:

f2c2 7297 movt

r2, #10135; 0x2797

832c:

f7ff efe8

8300 < init+0x3c>

blx

return 0;

8330:

2000

r0, #0

movs

8332:

bd08

{r3, pc}

pop

int multiply(int a, int b)

000083ac <multiply>:

83ac:

fb01 f000

mul.w

r0, r1, r0

return (a*b);

83b0:

4770

bx

lr

83b2:

bf00

nop

221412523*3 = 664237569 or

0x27977601

```

#### Example 6.c

```

int main(void)

{

int a, b;

a = 6;

...

// Important: Subtraction taking place

b = a - 182947;

...

printf("a's negatory is %d\n", b);

return 0;

}

```

Before the subtraction operation

```

CPSR = 0x60000010

```

After the subtraction operation

```

0000838c <main>:

838c:

b590

push

{r4, r7, lr}

838e:

b085

sub

sp, #20

8390:

af00

add

r7, sp, #0

f04f 0306

8392:

r3, #6

mov.w

8396:

60fb

r3, [r7, #12]

str

8398:

f3ef 8400

r4, CPSR

mrs

839c:

60bc

str

r4, [r7, #8]

68fa

839e:

r2, [r7, #12]

ldr

83a0:

f243 535d movw

r3, #13661; 0x355d

83a4:

f6cf 73fd

r3, #65533 : 0xfffd

movt

83a8:

18d3

adds

r3, r2, r3

607b

83aa:

str

r3, [r7, #4]

f3ef 8400

r4, CPSR

83ac:

mrs

83b0:

603c

r4, [r7, #0]

str

f248 4344 movw

83b2:

r3, #33860; 0x8444

83b6:

f2c0 0300

r3, #0

movt

83ba:

4618

mov

r0, r3

83bc:

6879

ldr

r1, [r7, #4]

```

---

#### Reversing byte order

- REV reverses byte order (& endianness) of value in register and stores into destination register

- REV16 reverses byte order of each 16-bit halfword in register and stores into destination register

- REVSH reverses byte order of lower 16-bit halfword in register, sign extends to 32 bits and store into destination register

#### **REV & REV16 operations**

INSTRUCTION: rev r0, r0 rev16 r0, r0

R0

**CPSR**

**OxFFDECDAB**

0x20000010

**OxCDABFFDE**

0x20000010

R0

**OxABCDDEFF**

**CPSR**

0x20000010

**OxABCDDEFF**

0x20000010

#### Current Program Status Register

- N Negative flag

- Z Zero flag

- C Carry flag

- V Overflow flag

- Q Sticky overflow

- I 1: Disable IRQ mode

- F 1: Disable FIQ mode

- T 0: ARM state

- 1: Thumb state

- MODE Mode bits

#### Logical & Comparison operations

- AND Bitwise AND

- BIC Bitwise bit clear

- EOR Bitwise Exclusive OR

- ORR Bitwise OR

- ORN Bitwise OR NOT

- CMP Compare. SUB but with NO destination. (Same as SUBS)

- CMN Compare Negative. ADD but with NO destination. (Same as ADDS)

- TEQ Test Equivalence. Like EOR but with NO destination.

- TST Test. Like AND but with NO destination.

## Example 7.1.c

# Example 7.2.c

```

int main(void)

int a, b, d;

a = 221412523;

b = 374719560;

d = orr(a,b);

printf("a | b is %d\n", d);

return 0;

000083d0 <orr>:

int orr(int a, int b)

r0, r1

83d0: 4308

orrs

83d2: 4770

lr

bx

return (a|b);

```

## Example 7.3.c

```

int main(void)

int a, b, d;

a = 8;

b = 9:

if((a ^ b) > 0)

d = add(a,b);

else

d = subtract(b,a);

printf("a & b is %d\n", d);

return 0;

int add(int a, int b)

return (a+b);

int subtract(int a, int b)

return (a-b);

```

```

0000838c < main > :

orolog> ...

f04f 0308

8392:

mov.w

r3, #8

8396:

60bb

r3, [r7, #8]

str

8398:

f04f 0309

r3, #9

mov.w

839c:

607b

r3, [r7, #4]

str

r4, CPSR

839e:

f3ef 8400

mrs

83a2:

603c

r4, [r7, #0]

str

68ba

83a4:

ldr

r2, [r7, #8]

83a6:

687b

r3, [r7, #4]

ldr

83a8:

4053

r3, r2

eors

83aa:

2b00

r3, #0

cmp

dd05

83ac:

83ba <main+0x2e>

ble.n

68b8

83ae:

ldr

r0, [r7, #8]

83b0:

6879

r1, [r7, #4]

ldr

83b2:

f000 f829

bl

8408 <add>

83b6:

60f8

str

r0, [r7, #12]

83b8:

e004

83c4 <main+0x38>

b.n

83ba:

6878

ldr

r0, [r7, #4]

83bc:

68b9

ldr

r1, [r7, #8]

83be:

f000 f831

bl

8424 <subtract>

83c2:

60f8

str

r0, [r7, #12]

<contd>...

```

#### **BIC**

- BIC clears the bits specified in a mask

- For example,

- R0 = 0x57 or 0b0101 0111

- R1 = 0x24 or 0b0010 0100

- BIC <R2> <R0> <R1>

- Means R2 = R0 &  $^{\sim}$ (R1) = 0b0101 0011 or 0x53

- Mask can also be a shifted value (using Shift operations)

#### Memory operations Part I

- LDR Load data from memory into registers

- STR Store data from registers to memory

- Caveat: LDR/STR can load/store data on a boundary alignment that is the same as the data type size being loaded/stored.

- LDR can only load 32-bit words on a memory address that is multiples of 4 bytes.

#### Memory Operations Part I contd...

- LDR r0, [r1] loads r0 with contents of memory address pointed to by r1

- STR r0, [r1] stores the contents of r0 to the memory address pointed to by r1.

- Warning: This can be confusing since destination is actually specified in the second argument

- Also LDR r0, [r1, #4] means

- r0 = [r1 + 4] and r1 value remains unchanged

- Similarly STR r0, [r1, #4] means

- [r1+4] = r0 and r1 value remains unchanged

- The above two instructions addressing mode is called pre-indexed addressing

#### Example 8.c

```

int main(void)

{

int a, b;

int *x;

a = 8;

b = 9;

x = &a;

b = *x + 2;

printf("The address of a is 0x%x\n",x);

printf("The value of b is now %d\n",b);

return 0;

}

```

```

0000838c <main>:

b580

838c:

push

{r7, lr}

838e:

b084

sp, #16

sub

8390:

af00

r7, sp, #0

add

8392:

f04f 0308

r3, #8

mov.w

8396:

607b

r3, [r7, #4]

str

8398:

f04f 0309

r3, #9

mov.w

839c:

60fb

r3, [r7, #12]

str

839e:

f107 0304

r3, r7, #4

add.w

83a2:

60bb

r3, [r7, #8]

str

83a4:

68bb

r3, [r7, #8]

ldr

83a6:

681b

r3, [r3, #0]

ldr

83a8:

f103 0302

add.w

r3, r3, #2

60fb

83ac:

r3, [r7, #12]

str

83ae:

f248 4330

r3, #33840

; 0x8430

movw

83b2:

f2c0 0300

r3, #0

movt

83b6:

4618

r0, r3

mov

83b8:

68b9

ldr

r1, [r7, #8]

f7ff ef92

82e0 < init+0x20>

83ba:

blx

83be:

f248 434c

r3, #33868 ; 0x844c

movw

83c2:

f2c0 0300

movt

r3, #0

83c6:

4618

r0, r3

mov

83c8:

68f9

ldr

r1, [r7, #12]

83ca:

f7ff ef8a

82e0 < init+0x20>

blx

83ce:

f04f 0300

r3, #0

mov.w

83d2:

4618

mov

r0, r3

83d4:

f107 0710

r7, r7, #16

add.w

83d8:

46bd

sp, r7

mov

83da:

bd80

{r7, pc}

pop

```

#### Memory operations Part I contd...

- R7 in the previous example is known as base address register, where the base address register can by any one of R0-R12, SP, or LR

- We will cover consecutive multiple loads in one instruction later

#### Control Flow operations (Table A4-1)

| Instruction         | Description                                                 | Thumb mode range  | ARM mode range |

|---------------------|-------------------------------------------------------------|-------------------|----------------|

| B <label></label>   | Branch to target address                                    | +/- 16 MB         | +/- 32 MB      |

| BL, BLX <imm></imm> | Call a subroutine Call a subroutine, change instruction set | +/- 16 MB         | +/- 32 MB      |

| BLX <reg></reg>     | Call a subroutine, optionally change instruction set        | Any               | Any            |

| ВХ                  | Branch to target address, change instruction set            | Any               | Any            |

| CBZ                 | Compare and Branch on Zero                                  | 0-126 bytes       | Does not exist |

| CBNZ                | Compare and Branch on Nonzero                               | 0-126 bytes       | Does not exist |

| ТВВ                 | Table Branch (byte offsets)                                 | 0-510 bytes       | Does not exist |

| ТВН                 | Table Branch (halfword offsets)                             | 0-131070<br>bytes | Does not exist |

# **Conditional Branching**

- BLE: Branch if less than or equal

- Z=1 OR N!=V

- BGT: Branch if greater than

- Z=0 AND N=V

- BEQ: Branch if equal

- Z = 1

- BNE: Branch if not equal

- Z = 0

- How do N and V flags tell us if something is less or greater than?

- Generally there is a CMP or TST instruction before

- CMP <r0> <r1> means perform <r0> <r1>

### Example 9.s

```

0000835c < libc_csu_init>:

835c:

e92d 43f8 stmdb

sp!, {r3, r4, r5, r6, r7, r8, r9, lr}

8360:

4606

r6, r0

mov

8362:

f8df 9034

ldr.w

r9, [pc, #52]

; 8398 < libc csu init+0x3c>

8366:

460f

r7, r1

mov

8368:

4d0c

ldr

r5, [pc, #48]

; (839c < __libc_csu_init+0x40>)

836a:

4690

mov

r8, r2

836c:

44f9

add

r9, pc

836e:

f7ff ff91

bl

8294 < init>

8372:

447d

r5, pc

add

8374:

ebc5 0909 rsb

r9, r5, r9

8378:

ea5f 09a9 movs.w

r9, r9, asr #2

837c:

8392 < libc csu init+0x36>

d009

beq.n

837e:

2400

movs

r4, #0

8380:

f855 3b04

r3, [r5], #4

ldr.w

8384:

4630

r0, r6

mov

8386:

4639

r1, r7

mov

8388:

4642

r2, r8

mov

838a:

3401

adds

r4, #1

838c:

4798

r3

blx

838e:

454c

r4, r9

cmp

d1f6

8390:

8380 < __libc_csu_init+0x24>

bne.n

8392:

e8bd 83f8

Idmia.w

sp!, {r3, r4, r5, r6, r7, r8, r9, pc}

8396:

bf00

nop

8398:

00008ba0

0x00008ba0

.word

839c:

00008b96 .word

0x00008b96

```

### Current Program Status Register

- N Negative flag

- Z Zero flag

- C Carry flag

- V Overflow flag

- Q Sticky overflow

- I 1: Disable IRQ mode

- F 1: Disable FIQ mode

- T 0: ARM state

- 1: Thumb state

- MODE Mode bits

# Hello, World! in ARM Assembly

```

.text

start: .global start

@ sys write (fd, pstr, len)

@ r7=4 r0 r1 r2

mov r0, #1 @ fd <- stdout

adr r1, msg @ pstr <- *msg

mov r2, #14 @ len <- 14

mov r7, #4 @ syscall <- sys write

swi 0 @ system call

@ sys exit (exitcode)

@ r7=1 r0

mov r0, #0 @ exitcode <- 0

mov r7, #1 @ syscall <- sys exit

swi 0 @ system call

msg:

.asciz "Hello, world!\n"

.end

```

Linux GNUEABI spec means syscall identifier is put in R7 and arguments in RO-R6

Linux kernel ignores #imm value after SWI instruction

Syscall invoked with SWI/SVC instruction (supervisor mode)

#### Instructions covered so far...

- NOP

- ADD, ADC, SUB, SBC, RSB, RSC

- ASR, LSL, LSR, ROR, RRX

- MOV, MVN

- REV, REVSH, REV16

- AND, EOR, ORR, ORN, CMP, CMN

- BIC, TEQ, TST

- B, BL, BLX, BLE, BGT

- SWI

#### Hints on how to RTFM

- {S} updates flags in the CPSR

- {<c>} allows mnemonic of conditional to be added

- {<q>} instruction suffix with either:

- N Narrow, assembler must use 16-bit encoding for the intruction

- .W Wide, assembler must use 32-bit encoding for the instruction

- Do not use the .N or .W in your assembly code.

- As per manual, it will throw errors. Assembler decides on encoding depending on options selected.

#### Lab 1

Again commands given below for copying files into and out of the simulator

```

scp –P 2200 <localfile> root@localhost:/path/to/file scp –P 2200 root@localhost:/path/to/file <localfile> Password is passw0rd

```

- Fibonacci program

- Write assembly function to calculate fibonacci value at a given position x

- R0 has x

- For example: [0, 1, 2, 3, 4, 5, 6 ...] x

[0, 1, 1, 2, 3, 5, 8 ...] fibonacci(x)

- Only modify fib.s

# Sample algorithms

```

// Non-recursive

int fibonacci(int x) {

int previous = -1;

int result = 1;

int i=0;

int sum=0;

for (i = 0; i <= x; i++) {

sum = result + previous;

previous = result;

result = sum;

}

return result;

}</pre>

```

```

// Recursive

int fibonacci(int x) {

if(x<=0) return 0;

if(x==1) return 1;

return fibN(x-1) + fibN(x-2);

}</pre>

```

NOTE: Filler code follows Recursive algorithm.

#### Possible solution

```

fibonacci:

push {r3, r4, r5, lr}; function prolog

: r4 = r0 - 0

subs r4, r0, #0

ble .L3 ; if (r0 \le 0) goto .L3

cmp r4, #1

; Compare r4 to 1

beq .L4 ; if (r4 == 1) goto .L4

add r0, r4, \#4294967295; r0 = r4 + 4294967295 (or \#0xFFFFFFFF)

bl fibonacci

; goto fibonacci @PC relative address

mov r5, r0

; r5 = r0

sub r0, r4, #2 ; r0 = r4 - 2

bl fibonacci

; goto fibonacci @PC relative address

adds r0, r5, r0

pop {r3, r4, r5, pc}

.L3:

mov r0, #0

pop {r3, r4, r5, pc}

.L4:

mov r0, #1

pop {r3, r4, r5, pc}

```

#### DAY 1 PART 2

# Ah the old joke...

Source: <a href="http://xkcd.com/138/">http://xkcd.com/138/</a>

#### Memory operations Part I reminder...

- LDR r0, [r1]

- R1 in this example is known as base address register, where the base address register can be any one of R0-R12, SP, or LR

# Memory Operations Part II: Indexing operations

- Preindex with Writeback (denoted by [Rn,offset]!)

- Calculates address in base register + offset

- Uses calculated address for operation into Rn

- Stores the calculated address into base register

- Preindex (denoted by [Rn,offset])

- Calculates address in base register + offset

- Uses calculated address for operation into Rn

- Does NOT store the calculated address into base register

- Postindex (denoted by [Rt])

- Uses address in base register for operation into Rn

- Calculates address in base register + offset

- Stores the calculated address into base register

# LDR Indexing

| Indexing mode              | Instruction               | R0                     | R1 or Rbase          |

|----------------------------|---------------------------|------------------------|----------------------|

| Preindex with<br>Writeback | LDR r0, [r1, #2]!         | r0 = [r1 + 2]          | r1 = r1 + 2          |

|                            | LDR r0, [r1, r2]!         | r0 = [r1 + r2]         | r1 = r1 + r2         |

|                            | LDR r0, [r1, r2, LSL #3]! | r0 = [r1 + (r2 LSL 3)] | r1 = r1 + (r2 LSL 3) |

| Preindex                   | LDR r0, [r1, #2]          | r0 = [r1 + 2]          | r1 = r1              |

|                            | LDR r0, [r1, r2]          | r0 = [r1 + r2]         | r1 = r1              |

|                            | LDR r0, [r1, r2, LSL #3]  | r0 = [r1 + (r2 LSL 3)] | r1 = r1              |

| Postindex                  | LDR r0, [r1], #2          | r0 = [r1]              | r1 = r1 + 2          |

|                            | LDR r0, [r1], r2          | r0 = [r1]              | r1 = r1 + r2         |

|                            | LDR r0, [r1], r2, LSL #3  | r0 = [r1]              | r1 = r1 + (r2 LSL 3) |

Instruction form: LDR<c> <Rt>, [<Rn>{, offset}] where [] denotes memory contents of

# STR indexing

| Indexing mode              | Instruction               | Rt                     | Rn or Rbase          |

|----------------------------|---------------------------|------------------------|----------------------|

| Preindex with<br>Writeback | STR r0, [r1, #2]!         | [r1 + 2] = r0          | r1 = r1 + 2          |

|                            | STR r0, [r1, r2]!         | [r1 + r2] = r0         | r1 = r1 + r2         |

|                            | STR r0, [r1, r2, LSL #3]! | [r1 + (r2 LSL 3)] = r0 | r1 = r1 + (r2 LSL 3) |

| Preindex                   | STR r0, [r1, #2]          | [r1 + 2] = r0          | r1 = r1              |

|                            | STR r0, [r1, r2]          | [r1 + r2] = r0         | r1 = r1              |

|                            | STR r0, [r1, r2, LSL #3]  | [r1 + (r2 LSL 3)] = r0 | r1 = r1              |

| Postindex                  | STR r0, [r1], #2          | [r1] = r0              | r1 = r1 + 2          |

|                            | STR r0, [r1], r2          | [r1] = r0              | r1 = r1 + r2         |

|                            | STR r0, [r1], r2, LSL #3  | [r1] = r0              | r1 = r1 + (r2 LSL 3) |

Instruction form: STR<c> <Rt>, [<Rn>{, offset}] where [] denotes memory contents of

# Example 10 (Any program)

| 00008318 | <main>:</main> |      |                    | 00008334   | <_start>:  |        |                   |

|----------|----------------|------|--------------------|------------|------------|--------|-------------------|

| 8318:    | b508           | push | {r3, lr}           | 8334:      | f04f 0b00  | mov.w  | fp, #0            |

| 831a:    | 2001           | movs | r0, #1             | 8338:      | f04f 0e00  | mov.w  | Ir, #0            |

| 831c:    | f248 4108      | movw | r1, #33800; 0x8408 | 833c:      | f85d 1b04  | ldr.w  | r1, [sp], #4      |

| 8320:    | f247 6201      | movw | r2, #30209; 0x7601 | 8340:      | 466a       | mov    | r2, sp            |

| 8324:    | f2c0 0100      | movt | r1, #0             | 8342:      | f84d 2d04  | str.w  | r2, [sp, #-4]!    |

| 8328:    | f2c2 7297      | movt | r2, #10135; 0x2797 | 8346:      | f84d 0d04  | str.w  | r0, [sp, #-4]!    |

| 832c:    | f7ff efe8      | blx  | 8300 <_init+0x3c>  | 834a:      | f8df c014  | ldr.w  | ip, [pc, #20]     |

| 8330:    | 2000           | movs | r0, #0             | 8360 <_sta | rt+0x2c>   |        |                   |

| 8332:    | bd08           | рор  | {r3, pc}           | 834e:      | f84d cd04  | str.w  | ip, [sp, #-4]!    |

|          |                |      |                    | 8352:      | 4804       | ldr    | r0, [pc, #16]     |

|          |                |      |                    | (8364 <_st | art+0x30>) |        |                   |

|          |                |      |                    | 8354:      | 4b04       | ldr    | r3, [pc, #16]     |

|          |                |      |                    | (8368 <_st | art+0x34>) |        |                   |

|          |                |      |                    | 8356:      | f7ff efc6  | blx    | 82e4 <_init+0x20> |

|          |                |      |                    | 835a:      | f7ff efd8  | blx    | 830c <_init+0x48> |

|          |                |      |                    | 835e:      | 0000       | .short | 0x0000            |

|          |                |      |                    | 8360:      | 000083f9   | .word  | 0x000083f9        |

|          |                |      |                    | 8364:      | 00008319   | .word  | 0x00008319        |

|          |                |      |                    | 8368:      | 000083b5   | .word  | 0x000083b5        |

# A note on LDR/STR

- For loading large constants into registers, the assembler generally prefers using MOVN <Rd>, <#~large constant> (~ is Bitwise NOT)

- Assembler likes to use values between 0 and 255 along with barrel shifts to arrive at value

- Example:

- Instead of:LDR R0, #ffffff23MOVN R0, #0xDC

#### Other Instructions

- SSAT <reg1> <imm> <reg2> Signed Saturate

- USAT <reg1> <imm> <reg2> Unsigned Saturate

- QADD <reg1> <reg2> <reg3> Add & saturate

the result (<reg1> = sat(<reg2> + <reg3>)

- QSUB –Subtract & saturate the result

<reg1> = sat(<reg2> <reg3>)

- QDADD Saturate Double & Add <reg1>=sat (<reg2> + 2\*<reg3>)

- QDSUB <reg1> = sat(<reg2> 2\*<reg3>)

## Control Flow operations (Table A4-1)

| Instruction         | Description                                                                    | Thumb mode range    | ARM mode range |

|---------------------|--------------------------------------------------------------------------------|---------------------|----------------|

| B <label></label>   | Branch to target address                                                       | +/- 16 MB           | +/- 32 MB      |

| BL, BLX <imm></imm> | Call a subroutine Call a subroutine, change instruction set                    | +/- 16 MB           | +/- 32 MB      |

| BLX <reg></reg>     | Call a subroutine, optionally change instruction set                           | Any                 | Any            |

| ВХ                  | Branch to target address, change instruction set                               | Any                 | Any            |

| CBZ                 | Compare and Branch on Zero (16-bit) Permitted offsets are even from 0 – 126    | +4 to +130<br>bytes | Does not exist |

| CBNZ                | Compare and Branch on Nonzero (16-bit) Permitted offsets are even from 0 – 126 | +4 to +130<br>bytes | Does not exist |

| TBB                 | Table Branch (byte offsets) (32-bit)                                           | 0-510 bytes         | Does not exist |

| ТВН                 | Table Branch (halfword offsets) (32-bit)                                       | 0-131070<br>bytes   | Does not exist |

#### Conditional execution

- Most instructions can be made conditional by adding two letter mnemonic from table A8-1 to end of an existing instruction

- It increases performance by reducing the # of branches

- Example:

- ADDEQ r0, r1, r2; If zero flag is set then r0=r1+r2

### Conditional operations (Table A8-1)

| Suffix | Description             | Flags tested |

|--------|-------------------------|--------------|

| EQ     | Equal                   | Z=1          |

| NE     | Not Equal               | Z=0          |

| CS/HC  | Unsigned higher or same | C=1          |

| CC/LO  | Unsigned lower          | C=0          |

| MI     | Minus                   | N=1          |

| PL     | Positive or Zero        | N=0          |

| VS     | Overflow                | V=1          |

| VC     | No overflow             | V=0          |

| н      | Unsigned Higher         | C=1 AND Z=0  |

| LS     | Unsigned lower or same  | C=0 OR Z=1   |

| GE     | Greater or equal        | N=V          |

| LT     | Less than               | N!=V         |

| GT     | Greater than            | Z=0 AND N=V  |

| LE     | Less than or equal      | Z=1 OR N!=V  |

| AL     | Always                  |              |

### Current Program Status Register

- N Negative flag

- Z Zero flag

- C Carry flag

- V Overflow flag

- Q Sticky overflow

- I 1: Disable IRQ mode

- F 1: Disable FIQ mode

- T 0: ARM state

- 1: Thumb state

- MODE Mode bits

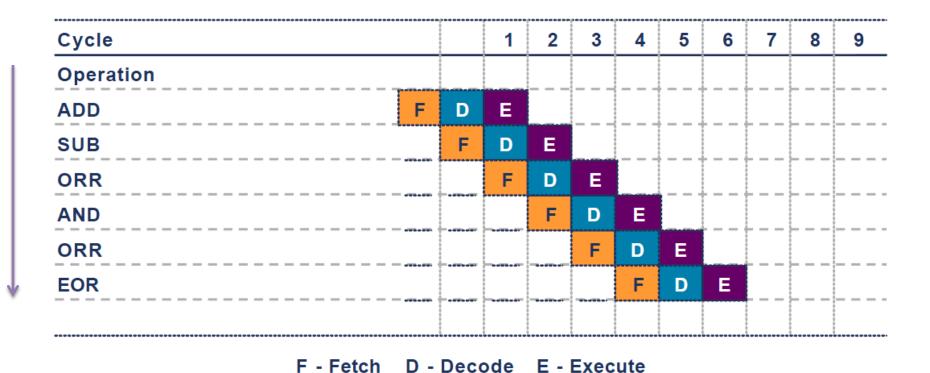

# **Pipelining**

- Does not decrease instruction execution time

- Increases throughput

- Time allocated dependent on longest cycle instruction

- Fetches and decodes instructions in parallel while executing current instruction.

#### Source:

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000-01/risc/pipelining/index.html

# Pipelining in action

Source: <a href="http://web.eecs.umich.edu/~prabal/teaching/eecs373-f10/readings/ARM">http://web.eecs.umich.edu/~prabal/teaching/eecs373-f10/readings/ARM</a> Architecture Overview.pdf

# Issues associated with pipelining

- Branch instructions

- Conditional execution reduces number of branches, which reduces # of pipeline flushes

- Instructions dependent on previous instructions (data-dependency)

- Interrupts in the beginning/middle/end of cycle?

- How code is optimized for pipelining is compiler & processor dependent

Source: <a href="http://bnrg.eecs.berkeley.edu/~randy/Courses/CS252.S96/Lecture08.pdf">http://bnrg.eecs.berkeley.edu/~randy/Courses/CS252.S96/Lecture08.pdf</a>

# Other ways of branching

- LDR PC, [PC, #offset]

- Value written has to be aligned for mode

- Earlier processors (armv4 and earlier) used to have prefetch

- PC points two instructions ahead

- Programmer has to account for PC+8

- Store address of branch location at current address + offset + 8

- Same tradition continues for all arm architectures so far

Source: <a href="http://en.wikipedia.org/wiki/List\_of\_ARM\_microprocessor\_cores">http://en.wikipedia.org/wiki/List\_of\_ARM\_microprocessor\_cores</a>

# Example 12.s

| 0x10000000    | add r0, r1, r2      |

|---------------|---------------------|

| 0x10000004    | ldr pc, [pc, #4]    |

| 0x10000008    | sub r1, r2, r3      |

| 0x1000000c    | cmp r0, r1          |

| 0x10000010    | 0x20000000          |

| •••           |                     |

| Branch target |                     |

| 0x20000000    | str r5, [r13, -#4]! |

#### ONE instruction to rule them all...

- LDM/STM Load multiple/Store multiple

- Used in conjunction with a suffix (called mode) for how to move consecutively

- Lowest register uses the lowest memory address

# LDM/STM modes

| Mode | Short description | LDM<br>synonym | STM<br>synonym | Start<br>Address | End<br>Address | Rn!    |

|------|-------------------|----------------|----------------|------------------|----------------|--------|

| IA   | Increment After   | P=0, U=1       | P=0, U=1       | Rn               | Rn<br>+4*N-4   | Rn+4*N |

| IB   | Increment Before  | P=1, U=1       | P=1, U=1       | Rn+4             | Rn+4*N         | Rn+4*N |

| DA   | Decrement after   | P=0, U=0       | P=0, U=0       | Rn-4*N<br>+4     | Rn             | Rn-4*N |

| DB   | Decrement before  | P=1, U=0       | P=1, U=0       | Rn-4*N           | Rn-4           | Rn-4*N |

| FA   | Full Ascending    | DA             | IB             |                  |                |        |

| EA   | Empty Ascending   | DB             | IA             |                  |                |        |

| FD   | Full Descending   | IA             | DB             |                  |                |        |

| ED   | Empty Descending  | IB             | DA             |                  |                |        |

N is the number of registers n goes from 1..N

# Stack operations

- Instead of POP, we use Load-Multiple

- Instead of PUSH, we use Store-Multiple

- Stacks can be

- (A)scending stack grows to higher memory addresses

- (D)escending stack grows to lower memory addresses

# LDM/STM pairs

| Store Multiple | Load Multiple |

|----------------|---------------|

| STMIA          | LDMDB         |

| STMIB          | LDMDA         |

| STMDA          | LDMIB         |

| STMDB          | LDMIA         |

# STMDB operation

INSTRUCTION: STMDB sp!, {r3, r4, r5, r7}

| R3 | 0xABCDDEFF |

|----|------------|

| R4 | 0x0000CAFE |

| R5 | 0xFEED0000 |

| R7 | 0xF00D0000 |

| SP | 0x00008018 |

| 0x8000 |            |

|--------|------------|

| 0x8004 |            |

| 0x8008 | 0xABCDDEFF |

| 0x800C | 0x0000CAFE |

| 0x8010 | 0xFEED0000 |

| 0x8014 | 0xF00D0000 |

| 0x8018 |            |

SP

0x00008008

# LDMIA operation

INSTRUCTION: LDMIA sp!, {r3, r4, r5, r7}

|    |            | 0x8000 |             |

|----|------------|--------|-------------|

|    |            | 0x8004 |             |

| R3 | 0xABCDDEFF | 0x8008 | 0xABCDDEFF  |

| R4 | 0x0000CAFE | 0x800C | 0x0000CAFE  |

| R5 | 0xFEED0000 | 0x8010 | 0xFEED0000  |

| R7 | 0xF00D0000 | 0x8014 | 0xF00D0000  |

|    |            |        | 0X1 00D0000 |

|    |            | 0x8018 |             |

|    |            |        |             |

| SP | 0x00008018 | SP     | 0x00008008  |

105

## Example 13.s

```

0000835c < libc_csu_init>:

835c:

e92d 43f8 stmdb

sp!, {r3, r4, r5, r6, r7, r8, r9, lr}

8360:

4606

r6, r0

mov

8362:

f8df 9034

ldr.w

r9, [pc, #52]

; 8398 < libc csu init+0x3c>

8366:

460f

r7, r1

mov

8368:

4d0c

ldr

r5, [pc, #48]

; (839c < __libc_csu_init+0x40>)

836a:

4690

mov

r8, r2

836c:

44f9

add

r9, pc

836e:

f7ff ff91

bl

8294 < init>

8372:

447d

r5, pc

add

8374:

ebc5 0909 rsb

r9, r5, r9

8378:

ea5f 09a9 movs.w

r9, r9, asr #2

837c:

d009

8392 < libc csu init+0x36>

beq.n

837e:

2400

movs

r4, #0

8380:

f855 3b04 ldr.w

r3, [r5], #4

8384:

4630

mov

r0, r6

8386:

4639

r1, r7

mov

8388:

4642

r2, r8

mov

838a:

3401

adds

r4, #1

838c:

4798

r3

blx

838e:

454c

r4, r9

cmp

8390:

d1f6

8380 < libc csu init+0x24>

bne.n

8392:

e8bd 83f8 Idmia.w

sp!, {r3, r4, r5, r6, r7, r8, r9, pc}

8396:

bf00

nop

8398:

00008ba0 .word

0x00008ba0

839c:

00008b96 .word

0x00008b96

```

# Switching between ARM and Thumb states

- A processor in Thumb can enter ARM state by executing any of the following:

- BX, BLX, or LDR/LDM operation on PC (R15)

- A processor in ARM can enter Thumb state by executing any of the following:

- ADC, ADD, AND, ASR, BIC, EOR, LSL, LSR, MOV, MVN, ORR, ROR, RRX, RSB, RSC, SBC, or SUB operation on PC (R15) and which does not set the condition flags.

#### Thumb2 instruction set means ...

- The instructions in Thumb2 itself are a mix of 16-bit and 32bit instructions and are run in <u>Thumb-mode</u>

- Compiler option to mix <u>ARM-mode</u> and <u>Thumb-mode</u> instructions: -m-thumb-interwork

- Default is –mno-thumb-interwork

- The Xeno Question So how can we tell the difference?

- Mentioned in the ATPCS manual (included in the references)

- The LSB (rightmost bit) of branch address has to be 1 if the instructions at that address are to be interpreted as Thumb2!

- If you want to jump to address containing a mix of 16-bit and 32-bit instructions make sure the address is odd.

# How does Thumb mode differentiate b/w 16-bit and 32-bit instructions?

- In Thumb mode ARM processor only reads halfword-aligned halfwords

- Looks at instruction encoding:

- If bits 15:11 of the halfword being decoded is one of following, then it is the first halfword of a 32 bit instruction

- 0b11101

- 0b11110

- 0b11111

- Otherwise, it is interpreted as 16-bit instruction

### ARM-Thumb Procedure Call Standard

- Followed by compilers

- Caller saved registers:

- The caller subroutine must preserve the contents of R0 – R3 if it needs them before calling another subroutine

- Callee saved registers:

- The called subroutine must preserve the contents of R4 – R11 (usually on the stack in memory) and must restore the values before returning (if used).

- What about interrupts?

# **ATPCS**

| Register | Synonym | Special  | Role in the procedure call standard                  |

|----------|---------|----------|------------------------------------------------------|

| r15      |         | PC       | The Program Counter. (x86 EIP)                       |

| r14      |         | LR       | The Link Register. (x86 saved EIP)                   |

| r13      |         | SP       | The Stack Pointer. (x86 ESP)                         |

| r12      |         | IP       | The Intra-Procedure-call scratch register. (x86 RSI) |

| r11      | v8      |          | Variable-register 8/Frame Pointer (x86 EBP)          |

| r10      | v7      |          | Variable-register 7/Stack Limit                      |

| r9       |         | v6/SB/TR | Platform specific register.                          |

| r8       | v5      |          | Variable-register 5.                                 |

| r7       | v4      |          | Variable-register 4. (can also be x86 EBP)           |

| r6       | v3      |          | Variable-register 3.                                 |

| r5       | v2      |          | Variable-register 2.                                 |

| r4       | v1      |          | Variable-register 1.                                 |

| r3       | a4      |          | Argument/scratch register 4.                         |

| r2       | a3      |          | Argument/scratch register 3.                         |

| r1       | a2      |          | Argument/result/scratch register 2.                  |

| r0       | a1      |          | Argument/result/scratch register 1. 111              |

### **ATPCS**

r0 r1 r2 **r**3 r4 r5 r6 **r**7 r8 r9 R10 (SL) r11 (FP) r12 (IP) r13 (SP) r14 (LR) r15 (PC)

Caller saved

Callee saved

FP is neither mandated nor precluded from use. If it is used, it must be Callee saved. In ARM state, R11 is used. In Thumb state, R4-R7 can be used.

Stack Pointer should be same upon Callee return as it was upon Callee entry. So should the Link Register!

## ATPCS in action

```

int main(void)

one();

return 0;

void one(void)

zero();

two();

return;

void two(void)

printf("main...one...two\n");

return;

void zero(void)

return;

```

```

int main(void)

{

r0-r3 saved.

call to one() made.

}

void one(void)

{

r4-r11 saved.

lr saved

fp saved to point to one above lr in stack

// use r0-r3 as arguments

two();

r4-r11, lr restored

bx lr (branches to lr)

}

```

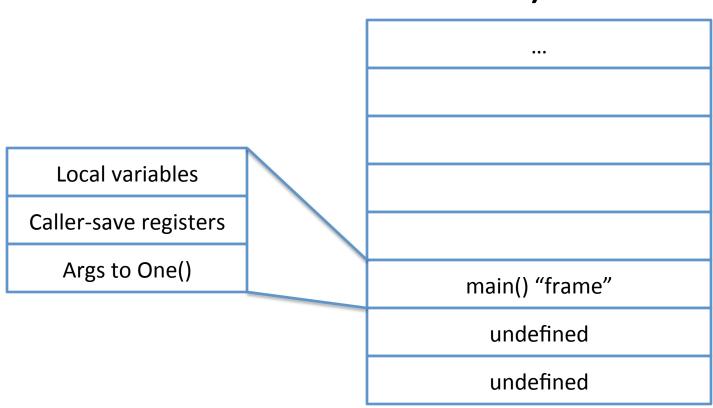

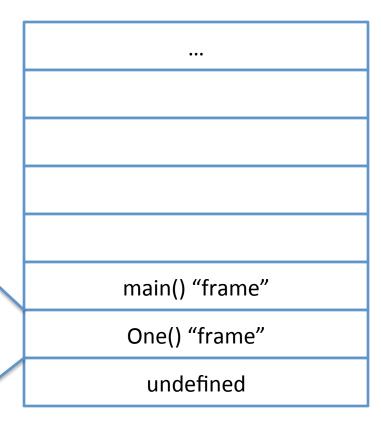

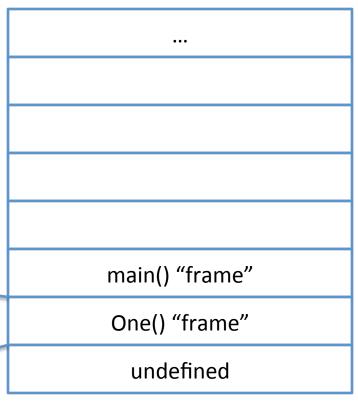

# So, how does this stack up? (pun intended)

# Branch with Link occurs to one()

# ARM now executing first instruction in

Callee-save registers are pushed onto stack using STMFD sp!, {registers} along with R14 (LR)

And R11/R7/R3(FP) can also be updated relative to (R13)SP

Local variables

Caller-save registers

Args to One()

LR = PC@main

Callee-save registers

one()

main() "frame"

One() "frame"

undefined

**Increasing Memory**

# ARM now executing second instruction in one()

Local variables are also added to the stack

Local variables

Caller-save registers

Args to One()

LR = PC@main

Callee-save registers

Local variables

main() "frame"

One() "frame"

undefined

# PC now about to branch to two()

Local variables

Caller-save registers

Args to One()

LR = PC@main

Callee-save registers

Local variables

Caller-save registers

Args to Two()

Caller-save registers for one() are saved. Arguments to two are also pushed

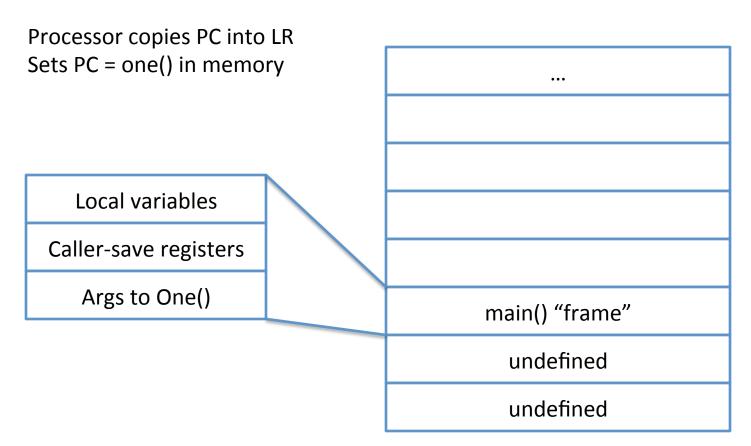

# Branch with Link occurs to two()

Processor copies PC into LR Sets PC = one() in memory

Local variables

Caller-save registers

Args to One()

LR = PC@main

Callee-save registers

Local variables

Caller-save registers

Args to Two()

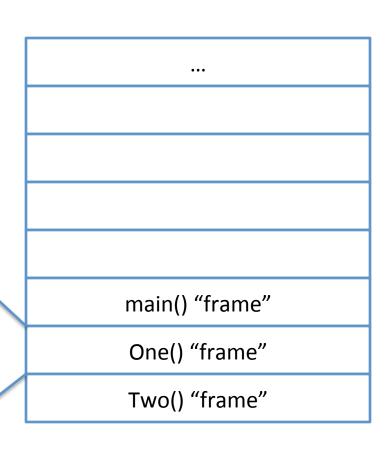

# ARM now executes first instruction in two()

Local variables

Caller-save registers

Args to One()

Callee-save registers

LR = PC@main()

Local variables

Caller-save registers

Args to Two()

LR = PC@One()

Callee-save registers

main() "frame"

One() "frame"

Two() "frame"

Saves the callee-save registers

Also saves the R14(Link Register)

# So, how did it stack up?

- Similar to x86 in some ways.

- However, R11(FP) is not really used much.

- SP is updated using STMFD and LDMFD

- Despite the return address being saved in the LR, most often it is put on the stack and then restored later directly into PC

- Which may help you in Lab 3...

# Current Program Status Register

- N Negative flag

- Z Zero flag

- C Carry flag

- V Overflow flag

- Q Sticky overflow

- I 1: Disable IRQ mode

- F 1: Disable FIQ mode

- T 0: ARM state

- 1: Thumb state

- MODE Mode bits

| _Mode [4:0] | Mode             |     |

|-------------|------------------|-----|

| 10000       | User             |     |

| 10001       | FIQ              |     |

| 10010       | IRQ              |     |

| 10011       | SVC (Supervisor) |     |

| 10111       | Abort            |     |

| 11011       | Undefined        |     |

| 11111       | System           | 122 |

### Generic ARM Modes

- User: Normal program execution mode

- FIQ: used for handling a high priority (fast) interrupt

- IRQ: used for handling a low priority (normal) interrupt

- Supervisor: entered on board reset and when a Software Interrupt instruction is executed

- Abort: used for handling memory access violations

- System: a privileged mode using same registers as User mode

#### User & System Mode

# **Banked Registers**

### **Arm Processor modes**

- User: normal program execution mode

- FIQ: used for handling a high priority (fast) interrupt

- IRQ: used for handling a low priority (normal) interrupt

- Supervisor: entered on reset and when SWI (software interrupt instruction) is executed

- Abort: used for handling memory access violations

- Undefined: used for handling undefined instructions

- System: a privileged mode that uses the same registers as the user mode

# ARMv7 Processor modes (Table B1-1)

| Processor<br>mode |     | Encoding | Privilege<br>Level | Implemented                     | Security State  | Instruction/Condition (if available) |

|-------------------|-----|----------|--------------------|---------------------------------|-----------------|--------------------------------------|

| User              | usr | 10000    | PL0                | Always                          | Both            |                                      |

| FIQ               | fiq | 10001    | PL1                | Always                          | Both            | INTERRUPT                            |

| IRQ               | irq | 10010    | PL1                | Always                          | Both            | INTERRUPT                            |

| Supervisor        | SVC | 10011    | PL1                | Always                          | Both            | SVC/SWI                              |

| Monitor           | mon | 10110    | PL1                | Security Extensions (TrustZone) | Secure only     | SMC/Secure Monitor Call EXCEPTION    |

| Abort             | abt | 10111    | PL1                | Always                          | Both            | Data/Prefetch Abort EXCEPTION        |

| Нур               | hyp | 11010    | PL2                | Virtualization<br>Extensions    | Non-secure only | HVC/EXCEPTION                        |

| Undefined         | und | 11011    | PL1                | Always                          | Both            | UNDEFINED                            |

| System            | sys | 11111    | PL1                | Always                          | Both            |                                      |

# Mode changing instructions

- SVC SuperVisor Call or SWI SoftWare Interrupt

- Changes mode to Supervisor mode

- SMC Secure Monitor Call

- Changes mode to Secure (with TrustZone)

- HVC Hypervisor Call

- Changes mode supervisor (with hardware virtualization extenstions)

# Switching modes

- Specific instructions for switching between processor modes (SVC/SWI etc.)

- HVC (Hypervisor call) only available with specific hardware support

- SMC (Secure Monitor call) also only available only with specific hardware support (TrustZone)

- MOVS PC, LR (copies SPSR to CPSR/APSR)

- Linux kernel and other RTOS ("rich featured" OS) run in Supervisor mode generally

- Remember the SWI from Hello World?

# Special instructions

- SUBS PC, LR, #<imm>

- Subtracts #<imm> value from LR and branches to resulting address

- It also copies SPSR to CPSR

- MOVS PC, LR

- Same as above but branches to address in LR and also copies SPSR to CPSR

- For use in returning to User/System mode from exception/interrupt modes

# How to read/write Status registers

- CPSR and APSR value can be saved into register

- MSR Move to Special register from ARM core register

- Example: msr <cpsr/apsr> <r0>

- MRS Move to ARM core Regsiter from special register

- Example: mrs <r0> <cpsr/apsr>

## **SCTLR** Register

- System Control Register: part of Coprocessor CP15 registers

- Allows controlling system wide settings such as:

- Mode (ARM/Thumb) for exceptions

- Base address for exception vector table

- Not fully emulated in kvm/qemu

- Different for different processor profiles

- Controls exception handling configurations

- Whether exceptions should be handled in ARM state or Thumb state

# SCTLR Register

- These settings are only available on Cortex-R and not on any others

- SCTLR.DZ = 0 means a Divide-by-Zero returns zero result

- SCTLR.DZ = 1 means a Divide-by-Zero generates and undefined instruction exception

- IE bit gives instruction endianness as implemented and is READ ONLY

# GNU Debugger (GDB) Intro

- The GNU debugger is a command line debugging tool

- A graphical frontend is also available called ddd

# GNU Debugger (GDB) intro

- Start gdb using:

- gdb <binary>

- Pass initial commands for gdb through a file

- gdb <binary> –x <initfile>

- For help

- help

- To start running the program

- run or r <argv>

## GDB initial commands